文章大綱

台積電推出的 CoWoS 封裝技術為了解決 AI 晶片所需要的高算力,因此採用 2.5D/3D 封裝來提升效率。

台積電 2.5D CoWoS 可以分成 CoWoS-S、CoWoS-R、CoWoS-L,差別在於中介層使用的材料以及可封裝的 HBM。

目前市面上主流為 CoWoS-S,不論是 AI 伺服器、高效能運算產品,例如:輝達的 H100 以及 AMD 的 MI300 皆使用 CoWoS-S,但缺點是生產成本過高。

CoWoS-R 透過 InFO 技術、中介層,將各 SoC、HBM 異質整合,取代了中介層中的矽穿孔,可進一步降低整體封裝成本,適合網通類產品使用。

CoWoS-L 為目前台積電最新技術,在矽中介層中加入主動元件 LSI,提升晶片設計及封裝彈性,可以堆疊多達 12 顆 HBM3,而成本比 CoWoS-S 還低,預計在 2024 年會推出,新一代 AI 晶片有機會使用,有望成為未來 CoWoS 技術主流。

CoWoS-S 是什麼?

CoWoS-S 是使用單片矽中介層和矽通孔(TSVs),實現晶片與基板之間的高速電信號直接傳輸,然而單片矽中介層容易存在良率問題。

CoWoS-R 是什麼?

CoWoS-R 利用 InFO 技術讓有機中介層替代 CoWoS-S 的矽中介層,有機中介層具有精細間距的 RDL,為 HBM(高帶寬記憶體)與 SoC 晶片或晶片與基板之間提供高速連接。

由於有機中介層本身具有柔韌性,由聚合物和銅線組成,充當壓力緩衝器,減少了基板與中介層之間熱膨脹係數不匹配引起的可靠性問題。

CoWoS-R 提供了優越的可靠性和良率,也可以使新的封裝可以擴展其尺寸,以滿足更複雜的功能需求。

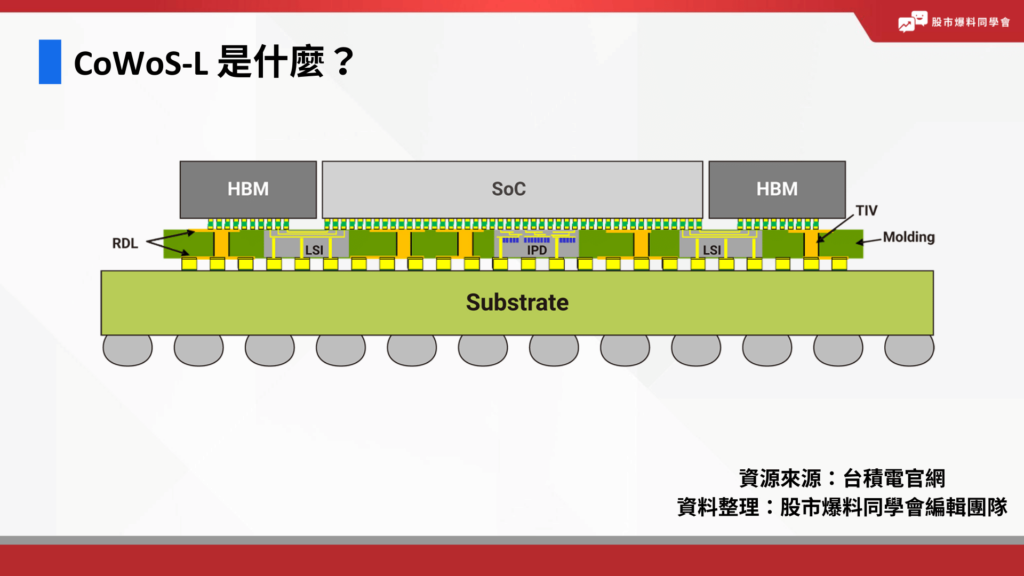

CoWoS-L 是什麼?

CoWoS-L 是 CoWoS 平台中的一種後置晶片封裝,結合 CoWoS-S 和 InFO 技術的優勢,使用 LSI(局部矽互連)晶片的中介層提供最靈活的整合,用於晶片間的互連和 RDL 層的電源和信號傳輸。

CoWoS-L 保留了 CoWoS-S 的吸引特徵,即矽通孔(TSVs),這也減少了使用大矽中介層在 CoWoS-S 中引起的良率問題。

在某些實際案例中,可能還會使用絕緣通孔(TIVs)代替 TSVs,以減少插入損耗。

該封裝從 1.5 倍光罩尺寸的中介層起步,配置 1 個 SoC 和 4 個 HBM 方塊,並將進一步擴展到更大尺寸以整合更多晶片。

CoWoS-L 服務的主要特點包括:

- 使用 LSI 晶片的高路由密度晶片間互連,通過多層次亞微米銅線進行互連。LSI 晶片可以在每個產品內實現多種連接架構(例如 SoC 對 SoC、SoC 對小晶片、SoC 對 HBM 等),並且可以在多個產品中重複使用。相應的金屬類型、層數和間距與 CoWoS-S 的提供一致。

- 基於模塑的中介層,在前側和後側都有寬間距的 RDL 層,並通過 TIV(中介層通孔)進行信號和電源傳輸,在高速傳輸中提供低損耗的高頻信號。

- 能夠整合額外元件,例如獨立的 IPD(集成無源器件),直接位於 SoC 晶片下方,以更好地支持其信號通信並改善 PI/SI(電源完整性/信號完整性)。

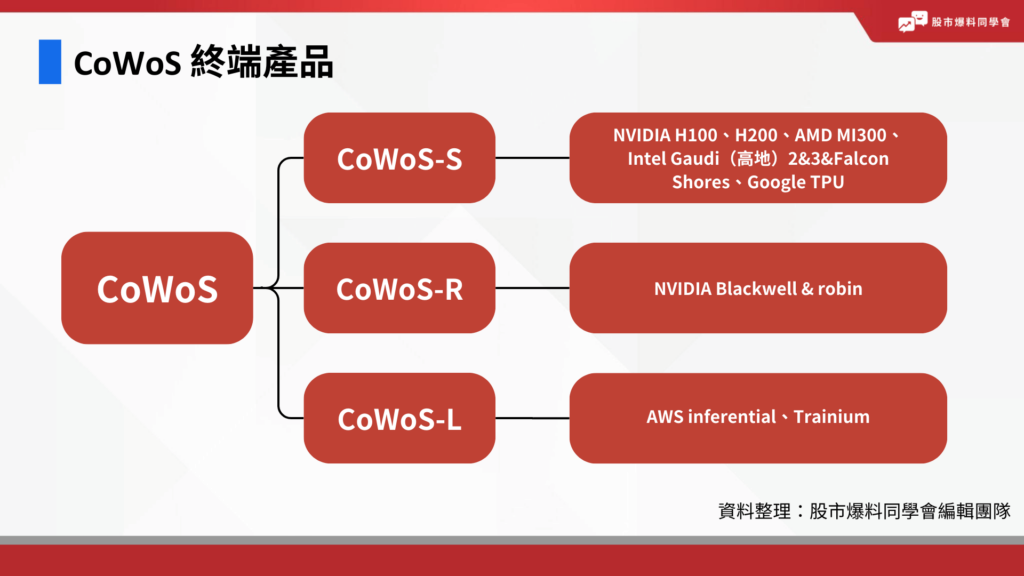

CoWoS 終端產品分布

CoWoS 目前大多都是用在 AI 相關的晶片、產品上面,目前已知或推論出來可能會採用 CoWoS 製成的產品如下:

- CoWoS-S:NVIDIA H100、H200、AMD MI300、Intel Gaudi(高地)2&3&Falcon Shores、Google TPU

- CoWoS-R:NVIDIA Blackwell & robin

- CoWoS-L:AWS inferential Trainium

CoWoS 先進封裝產能預估

台積電是目前唯一有能力量產中介層線寬、級距都小於 1mm 的晶圓代工廠,AI 高階伺服器例如:NVIDIA 的 H100、A100 以及 AMD 推出的 MI300 都受限於台積電 CoWoS 產能狀況,其中以 NVIDIA 佔據多數 CoWoS 產能。

目前台積電持續擴充相關設備,預計 2024 年第四季產能為每月 2.8 萬片,以應對 NVIDIA、AMD 的需求。

CoWoS 常見問題

CoWoS-R 是什麼?

CoWoS-R 是 CoWoS 高級封裝家族的一員,利用 InFO 技術使用 RDL 中介層,作為晶片之間的互連,特別是在 HBM(高帶寬記憶體)和 SoC 異質整合中。

CoWoS-L 是什麼?

CoWoS-L 是 CoWoS 平台中的一種後置晶片封裝,結合 CoWoS-S 和 InFO 技術的優勢,使用 LSI(局部矽互連)晶片的中介層提供最靈活的整合,用於晶片間的互連和 RDL 層的電源和信號傳輸。